Y

YoungC_Park

Mon, Jul 30, 2018 6:34 AM

Hi all,

I hope someone could help me on my situation. I could not find similar cases on the usrp archive.

I have one USRP X310 that has UBX-160(slot A) , LFTX board(slot B) and GPS module installed.

-

my UHD is 3.11.0

-

Using uhd API based on tx_samples from_file.cpp, I can generate dual output bursts from UBX160 and LFTX with 200MHz master clock and 100Msps on USRP X310.

-

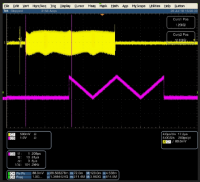

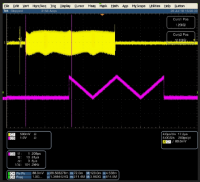

However, the second output (ch 1, red in the picture) is lagged from the first one (ch 0, yellow) by about (~10us with +-4us uncertainty)

-

The baseband burst is a sawtooth waveform of two cycles(2000 samples long). and UBX160 modulates it into fc = 1GHz whereas LFTX generates it as is.

-

This lagging is quite constant (10us) even if I change the sampling rate (10,20,50, 100MSps).

-

Tried 'Unknown PPS', 'gpsdo', 'internal',,, but no difference.

-

When I switch the order of channels to (1,0) as opposed to (0,1), then the ch0 lags behind the ch1, which seems that this is related to some sequenced process…

We are seeking for helps on the cause and cure about this lagging…

Thanks,

Young C. Park

Hi all,

I hope someone could help me on my situation. I could not find similar cases on the usrp archive.

I have one USRP X310 that has UBX-160(slot A) , LFTX board(slot B) and GPS module installed.

- my UHD is 3.11.0

- Using uhd API based on tx_samples from_file.cpp, I can generate dual output bursts from UBX160 and LFTX with 200MHz master clock and 100Msps on USRP X310.

- However, the second output (ch 1, red in the picture) is lagged from the first one (ch 0, yellow) by about (~10us with +-4us uncertainty)

- The baseband burst is a sawtooth waveform of two cycles(2000 samples long). and UBX160 modulates it into fc = 1GHz whereas LFTX generates it as is.

- This lagging is quite constant (10us) even if I change the sampling rate (10,20,50, 100MSps).

- Tried 'Unknown PPS', 'gpsdo', 'internal',,, but no difference.

- When I switch the order of channels to (1,0) as opposed to (0,1), then the ch0 lags behind the ch1, which seems that this is related to some sequenced process…

We are seeking for helps on the cause and cure about this lagging…

Thanks,

Young C. Park

FS

Fabian Schwartau

Mon, Jul 30, 2018 7:08 AM

Hi Young,

I am not an expert, but I have three suggestions:

- Using 'Unknown PSS' or any other sync method should not have no

affect, as this is for syncing two or more USRPs. You have only one FPGA

and that is in sync with itself ;)

- Did you tried using timed commands? (see function set_command_time())

- If that does not work, maybe the FPGA can handly only one command at

a time - even if you tell him to execute two. Then it may be possible to

start one command timed before the other and extend that sequence of

samples with the correct amount of zeros.

Best regards,

Fabian

Am 30.07.2018 um 08:34 schrieb YoungC_Park via USRP-users:

Hi all,

I hope someone could help me on my situation. I could not find similar

cases on the usrp archive.

I have one USRP X310 that has UBX-160(slot A) , LFTX board(slot B) and

GPS module installed.

-

my UHD is 3.11.0

-

Using uhd API based on tx_samples from_file.cpp, I can generate dual

output bursts from UBX160 and LFTX with 200MHz master clock and 100Msps

on USRP X310.

-

However, the second output (ch 1, red in the picture) is lagged from

the first one (ch 0, yellow) by about (~10us with +-4us uncertainty)

-

The baseband burst is a sawtooth waveform of two cycles(2000 samples

long). and UBX160 modulates it into fc = 1GHz whereas LFTX generates it

as is.

-

This lagging is quite constant (10us) even if I change the sampling

rate (10,20,50, 100MSps).

-

Tried 'Unknown PPS', 'gpsdo', 'internal',,, but no difference.

-

When I switch the order of channels to (1,0) as opposed to (0,1), then

the ch0 lags behind the ch1, which seems that this is related to some

sequenced process…

We are seeking for helps on the cause and cure about this lagging…

Thanks,

Young C. Park

USRP-users mailing list

USRP-users@lists.ettus.com

http://lists.ettus.com/mailman/listinfo/usrp-users_lists.ettus.com

Hi Young,

I am not an expert, but I have three suggestions:

1) Using 'Unknown PSS' or any other sync method should not have no

affect, as this is for syncing two or more USRPs. You have only one FPGA

and that is in sync with itself ;)

2) Did you tried using timed commands? (see function set_command_time())

3) If that does not work, maybe the FPGA can handly only one command at

a time - even if you tell him to execute two. Then it may be possible to

start one command timed before the other and extend that sequence of

samples with the correct amount of zeros.

Best regards,

Fabian

Am 30.07.2018 um 08:34 schrieb YoungC_Park via USRP-users:

> Hi all,

>

> I hope someone could help me on my situation. I could not find similar

> cases on the usrp archive.

>

> I have one USRP X310 that has UBX-160(slot A) , LFTX board(slot B) and

> GPS module installed.

>

> - my UHD is 3.11.0

>

> - Using uhd API based on tx_samples from_file.cpp, I can generate dual

> output bursts from UBX160 and LFTX with 200MHz master clock and 100Msps

> on USRP X310.

>

> - However, the second output (ch 1, red in the picture) is lagged from

> the first one (ch 0, yellow) by about (~10us with +-4us uncertainty)

>

> - The baseband burst is a sawtooth waveform of two cycles(2000 samples

> long). and UBX160 modulates it into fc = 1GHz whereas LFTX generates it

> as is.

>

> - This lagging is quite constant (10us) even if I change the sampling

> rate (10,20,50, 100MSps).

>

> - Tried 'Unknown PPS', 'gpsdo', 'internal',,, but no difference.

>

> - When I switch the order of channels to (1,0) as opposed to (0,1), then

> the ch0 lags behind the ch1, which seems that this is related to some

> sequenced process…

>

> We are seeking for helps on the cause and cure about this lagging…

>

> Thanks,

>

> Young C. Park

>

>

>

> _______________________________________________

> USRP-users mailing list

> USRP-users@lists.ettus.com

> http://lists.ettus.com/mailman/listinfo/usrp-users_lists.ettus.com

>

DK

Derek Kozel

Mon, Jul 30, 2018 3:45 PM

Hello Fabian and Young,

The suggestion about timed commands is on point, I think that is what is

missing. Using unknown PPS will not hurt as there are two radio blocks with

timekeepers and using the unknown PPS setting, or external or gpsdo if

installed, will ensure that they are aligned.

- If that does not work, maybe the FPGA can handly only one command at a

time - even if you tell him to execute two. Then it may be possible to

start one command timed before the other and extend that sequence of

samples with the correct amount of zeros.

Each radio channel has it's own queue for timed commands so it is possible

to schedule all channels simultaneously.

Derek

On Mon, Jul 30, 2018 at 8:08 AM, Fabian Schwartau via USRP-users <

usrp-users@lists.ettus.com> wrote:

Hi Young,

I am not an expert, but I have three suggestions:

- Using 'Unknown PSS' or any other sync method should not have no affect,

as this is for syncing two or more USRPs. You have only one FPGA and that

is in sync with itself ;)

- Did you tried using timed commands? (see function set_command_time())

- If that does not work, maybe the FPGA can handly only one command at a

time - even if you tell him to execute two. Then it may be possible to

start one command timed before the other and extend that sequence of

samples with the correct amount of zeros.

Best regards,

Fabian

Am 30.07.2018 um 08:34 schrieb YoungC_Park via USRP-users:

Hi all,

I hope someone could help me on my situation. I could not find similar

cases on the usrp archive.

I have one USRP X310 that has UBX-160(slot A) , LFTX board(slot B) and

GPS module installed.

-

my UHD is 3.11.0

-

Using uhd API based on tx_samples from_file.cpp, I can generate dual

output bursts from UBX160 and LFTX with 200MHz master clock and 100Msps on

USRP X310.

-

However, the second output (ch 1, red in the picture) is lagged from

the first one (ch 0, yellow) by about (~10us with +-4us uncertainty)

-

The baseband burst is a sawtooth waveform of two cycles(2000 samples

long). and UBX160 modulates it into fc = 1GHz whereas LFTX generates it as

is.

-

This lagging is quite constant (10us) even if I change the sampling

rate (10,20,50, 100MSps).

-

Tried 'Unknown PPS', 'gpsdo', 'internal',,, but no difference.

-

When I switch the order of channels to (1,0) as opposed to (0,1), then

the ch0 lags behind the ch1, which seems that this is related to some

sequenced process…

We are seeking for helps on the cause and cure about this lagging…

Thanks,

Young C. Park

USRP-users mailing list

USRP-users@lists.ettus.com

http://lists.ettus.com/mailman/listinfo/usrp-users_lists.ettus.com

Hello Fabian and Young,

The suggestion about timed commands is on point, I think that is what is

missing. Using unknown PPS will not hurt as there are two radio blocks with

timekeepers and using the unknown PPS setting, or external or gpsdo if

installed, will ensure that they are aligned.

> 3) If that does not work, maybe the FPGA can handly only one command at a

time - even if you tell him to execute two. Then it may be possible to

start one command timed before the other and extend that sequence of

samples with the correct amount of zeros.

Each radio channel has it's own queue for timed commands so it is possible

to schedule all channels simultaneously.

Derek

On Mon, Jul 30, 2018 at 8:08 AM, Fabian Schwartau via USRP-users <

usrp-users@lists.ettus.com> wrote:

> Hi Young,

>

> I am not an expert, but I have three suggestions:

> 1) Using 'Unknown PSS' or any other sync method should not have no affect,

> as this is for syncing two or more USRPs. You have only one FPGA and that

> is in sync with itself ;)

> 2) Did you tried using timed commands? (see function set_command_time())

> 3) If that does not work, maybe the FPGA can handly only one command at a

> time - even if you tell him to execute two. Then it may be possible to

> start one command timed before the other and extend that sequence of

> samples with the correct amount of zeros.

>

> Best regards,

> Fabian

>

> Am 30.07.2018 um 08:34 schrieb YoungC_Park via USRP-users:

>

>> Hi all,

>>

>> I hope someone could help me on my situation. I could not find similar

>> cases on the usrp archive.

>>

>> I have one USRP X310 that has UBX-160(slot A) , LFTX board(slot B) and

>> GPS module installed.

>>

>> - my UHD is 3.11.0

>>

>> - Using uhd API based on tx_samples from_file.cpp, I can generate dual

>> output bursts from UBX160 and LFTX with 200MHz master clock and 100Msps on

>> USRP X310.

>>

>> - However, the second output (ch 1, red in the picture) is lagged from

>> the first one (ch 0, yellow) by about (~10us with +-4us uncertainty)

>>

>> - The baseband burst is a sawtooth waveform of two cycles(2000 samples

>> long). and UBX160 modulates it into fc = 1GHz whereas LFTX generates it as

>> is.

>>

>> - This lagging is quite constant (10us) even if I change the sampling

>> rate (10,20,50, 100MSps).

>>

>> - Tried 'Unknown PPS', 'gpsdo', 'internal',,, but no difference.

>>

>> - When I switch the order of channels to (1,0) as opposed to (0,1), then

>> the ch0 lags behind the ch1, which seems that this is related to some

>> sequenced process…

>>

>> We are seeking for helps on the cause and cure about this lagging…

>>

>> Thanks,

>>

>> Young C. Park

>>

>>

>>

>> _______________________________________________

>> USRP-users mailing list

>> USRP-users@lists.ettus.com

>> http://lists.ettus.com/mailman/listinfo/usrp-users_lists.ettus.com

>>

>>

> _______________________________________________

> USRP-users mailing list

> USRP-users@lists.ettus.com

> http://lists.ettus.com/mailman/listinfo/usrp-users_lists.ettus.com

>

YC

Young C. Park

Tue, Jul 31, 2018 6:58 AM

Fabian and Derek,

Thanks for your comments,

Yesterday I realized that 10GbE could not support my 100MSymps, complex

dual channel output.

That's why I've seen underflow messages. I actually have got around this

underflow by putting (ms) delay between bursts.

However, it seems like that there's something going on even if I dont see

any underflow message after the delay..

So I'd like to know what happens how the buffers are managed especially in

2 channel case..

Q1 : In 2 channel case, does the tx buffer divided into half size ?

Q2 : Do the two tx buffers are filled up simultaneously or one after

another?

Q3 : when underflow happens, does the kernel wait until the 2 channel

buffers are filled up ? or it just starts to output as soon as the first

channel buffer is filled while the second is being filled?

If I got answers about these questions, the delayed output on the dual

channel can be explained more clearly...

Thanks,

Young C. Park

On Tue, Jul 31, 2018 at 12:45 AM, Derek Kozel via USRP-users <

usrp-users@lists.ettus.com> wrote:

Hello Fabian and Young,

The suggestion about timed commands is on point, I think that is what is

missing. Using unknown PPS will not hurt as there are two radio blocks with

timekeepers and using the unknown PPS setting, or external or gpsdo if

installed, will ensure that they are aligned.

- If that does not work, maybe the FPGA can handly only one command at

a time - even if you tell him to execute two. Then it may be possible to

start one command timed before the other and extend that sequence of

samples with the correct amount of zeros.

Each radio channel has it's own queue for timed commands so it is possible

to schedule all channels simultaneously.

Derek

On Mon, Jul 30, 2018 at 8:08 AM, Fabian Schwartau via USRP-users <

usrp-users@lists.ettus.com> wrote:

Hi Young,

I am not an expert, but I have three suggestions:

- Using 'Unknown PSS' or any other sync method should not have no

affect, as this is for syncing two or more USRPs. You have only one FPGA

and that is in sync with itself ;)

- Did you tried using timed commands? (see function set_command_time())

- If that does not work, maybe the FPGA can handly only one command at a

time - even if you tell him to execute two. Then it may be possible to

start one command timed before the other and extend that sequence of

samples with the correct amount of zeros.

Best regards,

Fabian

Am 30.07.2018 um 08:34 schrieb YoungC_Park via USRP-users:

Hi all,

I hope someone could help me on my situation. I could not find similar

cases on the usrp archive.

I have one USRP X310 that has UBX-160(slot A) , LFTX board(slot B) and

GPS module installed.

-

my UHD is 3.11.0

-

Using uhd API based on tx_samples from_file.cpp, I can generate dual

output bursts from UBX160 and LFTX with 200MHz master clock and 100Msps on

USRP X310.

-

However, the second output (ch 1, red in the picture) is lagged from

the first one (ch 0, yellow) by about (~10us with +-4us uncertainty)

-

The baseband burst is a sawtooth waveform of two cycles(2000 samples

long). and UBX160 modulates it into fc = 1GHz whereas LFTX generates it as

is.

-

This lagging is quite constant (10us) even if I change the sampling

rate (10,20,50, 100MSps).

-

Tried 'Unknown PPS', 'gpsdo', 'internal',,, but no difference.

-

When I switch the order of channels to (1,0) as opposed to (0,1), then

the ch0 lags behind the ch1, which seems that this is related to some

sequenced process…

We are seeking for helps on the cause and cure about this lagging…

Thanks,

Young C. Park

USRP-users mailing list

USRP-users@lists.ettus.com

http://lists.ettus.com/mailman/listinfo/usrp-users_lists.ettus.com

Fabian and Derek,

Thanks for your comments,

Yesterday I realized that 10GbE could not support my 100MSymps, complex

dual channel output.

That's why I've seen underflow messages. I actually have got around this

underflow by putting (ms) delay between bursts.

However, it seems like that there's something going on even if I dont see

any underflow message after the delay..

So I'd like to know what happens how the buffers are managed especially in

2 channel case..

Q1 : In 2 channel case, does the tx buffer divided into half size ?

Q2 : Do the two tx buffers are filled up simultaneously or one after

another?

Q3 : when underflow happens, does the kernel wait until the 2 channel

buffers are filled up ? or it just starts to output as soon as the first

channel buffer is filled while the second is being filled?

If I got answers about these questions, the delayed output on the dual

channel can be explained more clearly...

Thanks,

Young C. Park

On Tue, Jul 31, 2018 at 12:45 AM, Derek Kozel via USRP-users <

usrp-users@lists.ettus.com> wrote:

> Hello Fabian and Young,

>

> The suggestion about timed commands is on point, I think that is what is

> missing. Using unknown PPS will not hurt as there are two radio blocks with

> timekeepers and using the unknown PPS setting, or external or gpsdo if

> installed, will ensure that they are aligned.

>

> > 3) If that does not work, maybe the FPGA can handly only one command at

> a time - even if you tell him to execute two. Then it may be possible to

> start one command timed before the other and extend that sequence of

> samples with the correct amount of zeros.

>

> Each radio channel has it's own queue for timed commands so it is possible

> to schedule all channels simultaneously.

>

> Derek

>

> On Mon, Jul 30, 2018 at 8:08 AM, Fabian Schwartau via USRP-users <

> usrp-users@lists.ettus.com> wrote:

>

>> Hi Young,

>>

>> I am not an expert, but I have three suggestions:

>> 1) Using 'Unknown PSS' or any other sync method should not have no

>> affect, as this is for syncing two or more USRPs. You have only one FPGA

>> and that is in sync with itself ;)

>> 2) Did you tried using timed commands? (see function set_command_time())

>> 3) If that does not work, maybe the FPGA can handly only one command at a

>> time - even if you tell him to execute two. Then it may be possible to

>> start one command timed before the other and extend that sequence of

>> samples with the correct amount of zeros.

>>

>> Best regards,

>> Fabian

>>

>> Am 30.07.2018 um 08:34 schrieb YoungC_Park via USRP-users:

>>

>>> Hi all,

>>>

>>> I hope someone could help me on my situation. I could not find similar

>>> cases on the usrp archive.

>>>

>>> I have one USRP X310 that has UBX-160(slot A) , LFTX board(slot B) and

>>> GPS module installed.

>>>

>>> - my UHD is 3.11.0

>>>

>>> - Using uhd API based on tx_samples from_file.cpp, I can generate dual

>>> output bursts from UBX160 and LFTX with 200MHz master clock and 100Msps on

>>> USRP X310.

>>>

>>> - However, the second output (ch 1, red in the picture) is lagged from

>>> the first one (ch 0, yellow) by about (~10us with +-4us uncertainty)

>>>

>>> - The baseband burst is a sawtooth waveform of two cycles(2000 samples

>>> long). and UBX160 modulates it into fc = 1GHz whereas LFTX generates it as

>>> is.

>>>

>>> - This lagging is quite constant (10us) even if I change the sampling

>>> rate (10,20,50, 100MSps).

>>>

>>> - Tried 'Unknown PPS', 'gpsdo', 'internal',,, but no difference.

>>>

>>> - When I switch the order of channels to (1,0) as opposed to (0,1), then

>>> the ch0 lags behind the ch1, which seems that this is related to some

>>> sequenced process…

>>>

>>> We are seeking for helps on the cause and cure about this lagging…

>>>

>>> Thanks,

>>>

>>> Young C. Park

>>>

>>>

>>>

>>> _______________________________________________

>>> USRP-users mailing list

>>> USRP-users@lists.ettus.com

>>> http://lists.ettus.com/mailman/listinfo/usrp-users_lists.ettus.com

>>>

>>>

>> _______________________________________________

>> USRP-users mailing list

>> USRP-users@lists.ettus.com

>> http://lists.ettus.com/mailman/listinfo/usrp-users_lists.ettus.com

>>

>

>

> _______________________________________________

> USRP-users mailing list

> USRP-users@lists.ettus.com

> http://lists.ettus.com/mailman/listinfo/usrp-users_lists.ettus.com

>

>

--

------------------------

Youngcheol Park

ycpark.gt@gmail.com