usrp-users@lists.ettus.com

Discussion and technical support related to USRP, UHD, RFNoC

View all threadsRe: Center frequency drift on USRP B-series even with Octoclock

Hi Aneesh,

Thanks for your comment. I used a Intel(R) Core(TM) i7-8850H CPU for the

B-series experiment (which is somewhat weaker than the "AMD Ryzen 9

3900X 12-Core Processor" I used with the X310s, but the sampling rate

was only 1MHz in both cases, so it should be fine). The software is

basically a (self-made) JVM-based controller that communicates over

sockets with a (self-made) C++-based server that uses UHD 4.0 under the

hood. The whole thing is running on CentOS/Fedora. I attached the

terminal outputs in case it helps, but I don't see any overruns/underruns.

As for the use case, I'm trying to use this to compare phase offsets

across different receiver locations (given a fixed transmitter), so I

need a constant (and ideally zero) frequency offset, otherwise the IQ

vector keeps rotating back and forth as the frequencies drift apart.

Best regards,

Viktor

On 6/3/21 8:53 PM, aneesh patel wrote:

Viktor,

Cool benchmark.

Do you have some specifics on what's driving the b-series like host

CPU specs, software, any stdout output like overruns etc.?

There seems to be an issue with the external clock implementation on

the b series unless that's actually how it's supposed to look (!).

For the for factor, power, price, etc. I'd say the internal looks

pretty good for *most things.

Best of luck. Hopefully someone with experience chines in on the setup!

Aneesh

Sent from Yahoo Mail on Android

https://go.onelink.me/107872968?pid=InProduct&c=Global_Internal_YGrowth_AndroidEmailSig__AndroidUsers&af_wl=ym&af_sub1=Internal&af_sub2=Global_YGrowth&af_sub3=EmailSignature

On Thu, Jun 3, 2021 at 7:37 AM, Viktor Erdelyi

<viktor@ist.osaka-u.ac.jp> wrote:

Dear all,

First post here. I have done some measurements with USRP B-series

and X-series, and I noticed that, in the case of the B-series, the

center frequency drifts even with an Octoclock 10MHz REF. (The

drift is smaller than without Octoclock, though.) Is this

expected? Is the X-series just so much better, or is there

something else going on?

Details of the experiment:

* I sent a sine wave (constant I, constant Q) from one USRP to

another at 5.9GHz and looked at the spectrogram of the

received signal. The ideal result of such an experiment would

be a straight vertical line at 0 Hz (i.e. 5.9GHz).

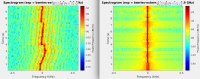

* I added an image of the relevant spectrograms below. The left

side of the figure is TX = USRP B205, RX = USRP B210, internal

vs. external (Octoclock) REF. The right side of the figure is

TX = USRP X310, RX = (another) USRP X310, internal vs.

external (Octoclock) REF.

* The two X310s have UBX-160 daughterboards.

* I check for LO_locked and ref_locked before doing TX/RX.

I would appreciate any insights.

Thanks,

Viktor

_______________________________________________

USRP-users mailing list -- usrp-users@lists.ettus.com

<mailto:usrp-users@lists.ettus.com>

To unsubscribe send an email to usrp-users-leave@lists.ettus.com

<mailto:usrp-users-leave@lists.ettus.com>

Great info and thanks for the use case. Makes sense for the precision you need for your situation.

Since really it's just IO, basic driver calls, and instrumentation and your specs support all of that (assuming no weird nuances / I say this to cover myself ha), your sample methods seems great.

Given there is no issue with the b-series hardware (I actually can't recall if that's in spec for real life use cases but I actually learned something here from looking at your charts if it is), it seems you need the higher precision X series to get right to work unless there is a whiz-bang solution for realtime clock drift corrections at the precision you need for the b-series.

Best of luck! Lots of experience in this forum.

Aneesh

Sent from Yahoo Mail on Android

On Thu, Jun 3, 2021 at 8:39 AM, Viktor Erdelyiviktor@ist.osaka-u.ac.jp wrote: _______________________________________________

USRP-users mailing list -- usrp-users@lists.ettus.com

To unsubscribe send an email to usrp-users-leave@lists.ettus.com

Different synthesizers have different phase noise properties.

I suspect that if so the same test at lower frequencies on the B2xx things will improve.

Also the external-clock PLL in the B205 is much poorer than on the other family members—B200 and B210.

Sent from my iPhone

On Jun 3, 2021, at 9:05 AM, aneesh patel via USRP-users usrp-users@lists.ettus.com wrote:

Great info and thanks for the use case. Makes sense for the precision you need for your situation.

Since really it's just IO, basic driver calls, and instrumentation and your specs support all of that (assuming no weird nuances / I say this to cover myself ha), your sample methods seems great.

Given there is no issue with the b-series hardware (I actually can't recall if that's in spec for real life use cases but I actually learned something here from looking at your charts if it is), it seems you need the higher precision X series to get right to work unless there is a whiz-bang solution for realtime clock drift corrections at the precision you need for the b-series.

Best of luck! Lots of experience in this forum.

Aneesh

Sent from Yahoo Mail on Android

On Thu, Jun 3, 2021 at 8:39 AM, Viktor Erdelyi

viktor@ist.osaka-u.ac.jp wrote:

USRP-users mailing list -- usrp-users@lists.ettus.com

To unsubscribe send an email to usrp-users-leave@lists.ettus.com

USRP-users mailing list -- usrp-users@lists.ettus.com

To unsubscribe send an email to usrp-users-leave@lists.ettus.com

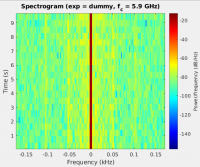

You're right Marcus, 0.9GHz seems to be better indeed (see image). Also

thanks for the input on the B205 PLL.

May I ask in what way phase noise can affect the signal's frequency?

According to an NI webpage [1], it "deals with very short time scales

and produces effects that look more like unwanted modulation changing

the shape of the waveform rather than a wandering frequency". Am I

missing something?

Thanks,

Viktor

Here's what phase noise does to the constellation points of a digital

modulation format (in this case, 64QAM).

phase noise

Ron

On 6/3/21 11:21 PM, Viktor Erdelyi wrote:

You're right Marcus, 0.9GHz seems to be better indeed (see image).

Also thanks for the input on the B205 PLL.

May I ask in what way phase noise can affect the signal's frequency?

According to an NI webpage [1], it "deals with very short time scales

and produces effects that look more like unwanted modulation changing

the shape of the waveform rather than a wandering frequency". Am I

missing something?

Thanks,

Viktor

USRP-users mailing list -- usrp-users@lists.ettus.com

To unsubscribe send an email to usrp-users-leave@lists.ettus.com

On Fri, Jun 4, 2021 at 2:21 AM Viktor Erdelyi viktor@ist.osaka-u.ac.jp

wrote:

You're right Marcus, 0.9GHz seems to be better indeed (see image). Also

thanks for the input on the B205 PLL.

May I ask in what way phase noise can affect the signal's frequency?

According to an NI webpage [1], it "deals with very short time scales and

produces effects that look more like unwanted modulation changing the shape

of the waveform rather than a wandering frequency". Am I missing something?

It should be noted the B205 doesn't really have an analog PLL like the

B200/B210/X-series. Check the schematic:

https://files.ettus.com/schematics/b200mini/b200mini.pdf

The VTCXO is fed by a 16-bit DAC and the FPGA does some counting to try to

keep it locked, but it doesn't have the feedback loop that the actual

analog PLL does.

Kind of comparing apples with oranges at that point.

Brian

For the record: I got my hands on a second B210, and I can confirm that,

in terms of keeping the center frequency synced, the B210+B210+Octoclock

combination indeed performs much better than the B205mini+B210+Octoclock

combination. Thanks for the insights!

Viktor

On 6/4/21 9:31 PM, Brian Padalino wrote:

On Fri, Jun 4, 2021 at 2:21 AM Viktor Erdelyi

<viktor@ist.osaka-u.ac.jp mailto:viktor@ist.osaka-u.ac.jp> wrote:

You're right Marcus, 0.9GHz seems to be better indeed (see image).

Also thanks for the input on the B205 PLL.

May I ask in what way phase noise can affect the signal's

frequency? According to an NI webpage [1], it "deals with very

short time scales and produces effects that look more like

unwanted modulation changing the shape of the waveform rather than

a wandering frequency". Am I missing something?

It should be noted the B205 doesn't really have an analog PLL like the

B200/B210/X-series. Check the schematic:

https://files.ettus.com/schematics/b200mini/b200mini.pdf

https://files.ettus.com/schematics/b200mini/b200mini.pdf

The VTCXO is fed by a 16-bit DAC and the FPGA does some counting to

try to keep it locked, but it doesn't have the feedback loop that the

actual analog PLL does.

Kind of comparing apples with oranges at that point.

Brian

USRP-users mailing list -- usrp-users@lists.ettus.com

To unsubscribe send an email to usrp-users-leave@lists.ettus.com